Table of Contents

brmCarramba

LowCost multiprocessor cluster based on cheap ARM MCU Cortex - M3 (in phase 1.)

Goals of this project

- Create low-cost multiprocessor computing device based on cheap ARM cpu ( LPC )

- Learn about multiprocessors device desing

Idea

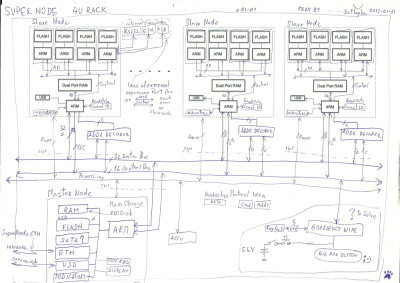

Device will contains slaveNodes, masterNode, storageNodes, this device is superNode, this superNode contains:

- slaveNodes - processors card

- masterNode - controller for internal communication between slaveNodes and external communication between superNodes

- storageNodes - card what have n. SD cards slots for storage, or SATA interfaces

slaveNode concept

each slaveNode have communication core and computing cores. Computing cores have one shared internal bus and access to dual port RAM. On other side DPRAM is communication core. This design allow use multiple design inside of slaveNode, cuz slaveNode is represented in superNode's internal bus by communication core. Then we can put on the slaveNode n. computing cores and doesn't matter if slaveNode have 4 computing cores or 128 cores or if computing cores have different architecture.

masterNode concept

masterNode is main controller for data interchange between slaveNodes (and superNodes, probably by ethernet interface (in future)).

Phases of project

Step #1

Case for brmCarramba

i choose al box what have profile inside, cuz i will put in this box card like slaveNode and masterNode .. this box can contains 11 pcb. Now i can desing PCB cuz i know real allowed sice of this PCB. Size is 20x103x53mm.

- 1455N1202BK HAMMOND - case

Part List

| No. | description | datasheet | one piece price | sum |

| 55x | LPC1343FBD48,151 - MCU, 32BIT, CORTEX M3, 48LQFP | LPC1343.pdf | 60.39Kc | 3321,45Kc |

| 1x | DAVICOM - DM9102DEP - IC, ENET CNTRL, 10/100M PHY, 128LQFP | DM9102DEP.pdf | 143.84Kc | 143.84Kc |

| 8x | stabilizator 3,3V LT1117CST-3.3#PBF. - IC, LDO VOLT REG, 3.3V, 0.8A | LT1117CST.pdf | 110.78Kc | 886,24Kc |